William Stallings Computer Organization and Architecture

Chapter 3 Instruction Cycle Review System Buses

## Function of Control Unit

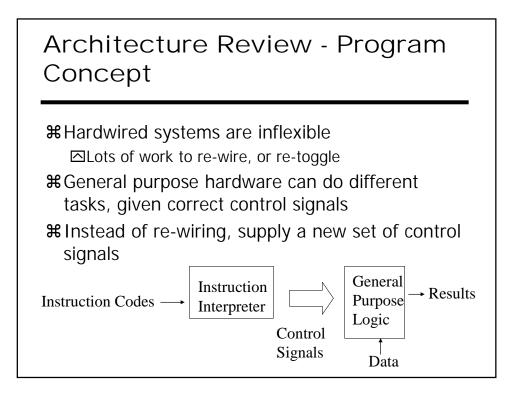

**¥**For each operation a unique code is provided □ e.g. ADD, MOVE

**#**A hardware segment accepts the code and issues the control signals

**#**We have a computer!

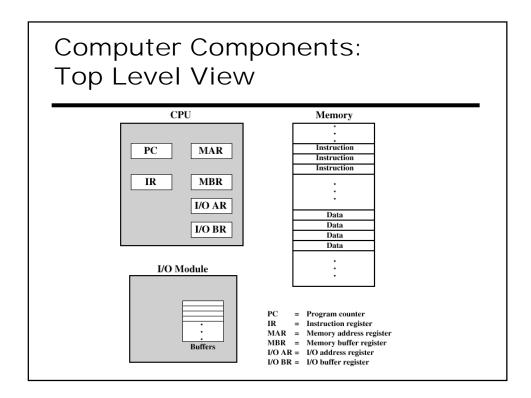

#### Components

Central Processing Unit

Control Unit

Arithmetic and Logic Unit

Data and instructions need to get into the CPU and results out

Input/Output

Temporary storage of code and results is needed

Main memory

# Processor-memory

data transfer between CPU and main memory

# Processor I/O

Data transfer between CPU and I/O module

# Data processing

Some arithmetic or logical operation on data

# Control

Alteration of sequence of operations

i.g. jump

# Combination of above

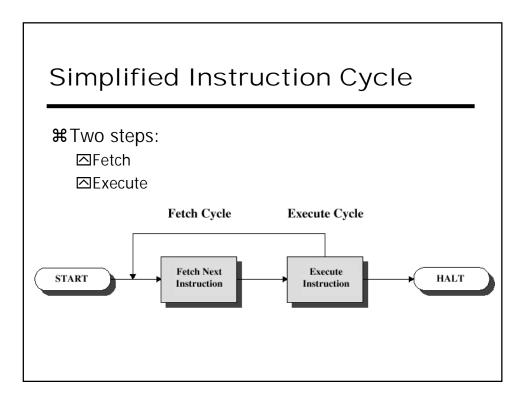

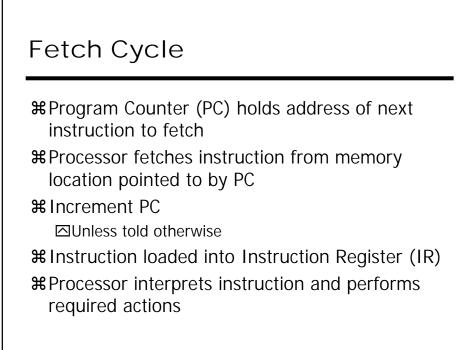

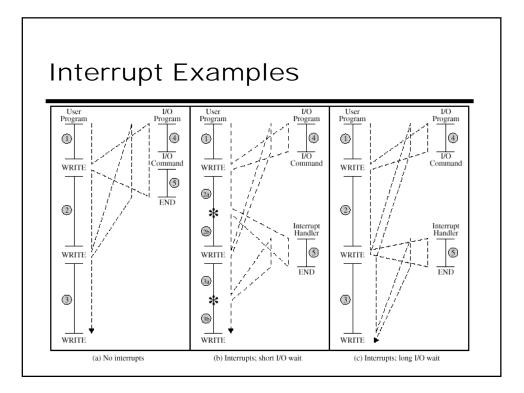

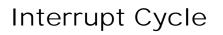

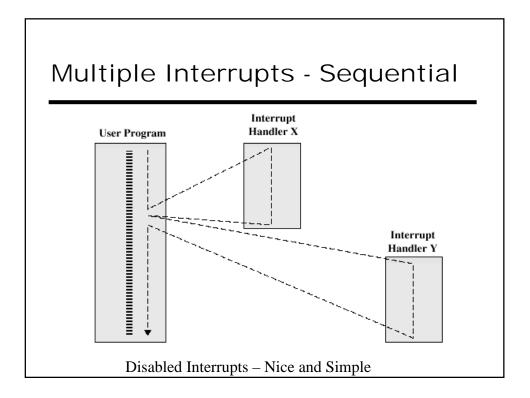

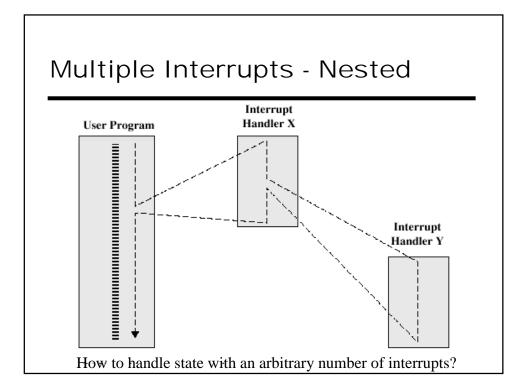

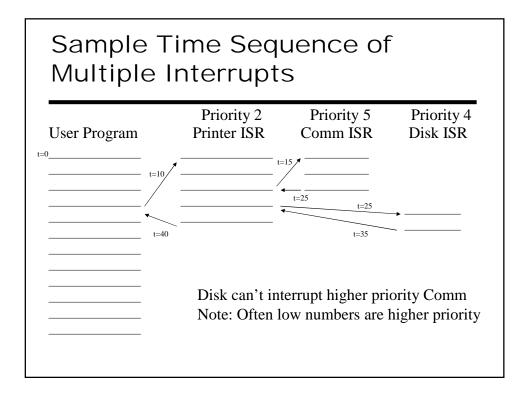

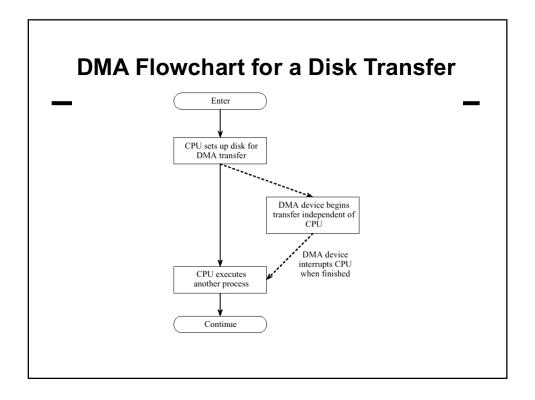

- **#** Added to instruction cycle

- # If no interrupt, fetch next instruction

## Connecting

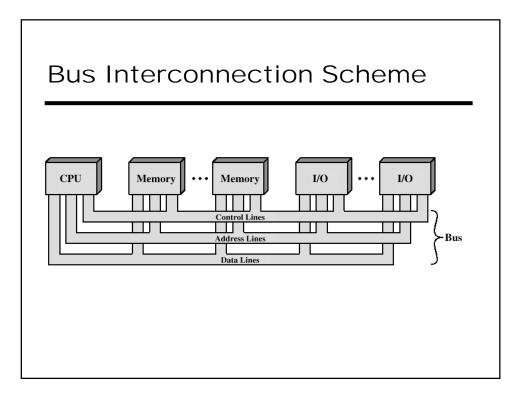

**¥** All the units must be connected **¥** Different type of connection for different type of unit

□ Memory

□ Input/Output

□ CPU

- # Memory typically consists of N words of equal length addressed from 0 to N-1

- ₭ Receives and sends data

△ To Processor

△ To I/O Device

- **#** Receives addresses (of locations)

- ₭ Receives control signals

- ⊠Read ⊡Write

- ⊡Timing

# Input/Output Connection(1)

₭ Functionally, similar to memory from internal viewpoint

- **#** Instead of N words as in memory, we have M ports

- ₩ Output

☐ Receive data from computer

☐ Send data to peripheral

₩ Input

☑ Receive data from peripheral☑ Send data to computer

## Input/Output Connection(2)

**#**Receive control signals from computer

Send control signals to peripherals ⊡e.g. spin disk

**#**Receive addresses from computer

- ⊠e.g. port number to identify peripheral

- #Send interrupt signals (control)

## **CPU** Connection

Sends control signals to other units

Reads instruction and data

Writes out data (after processing)

Receives (& acts on) interrupts

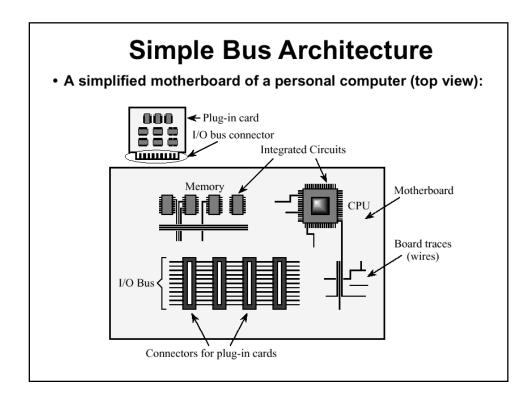

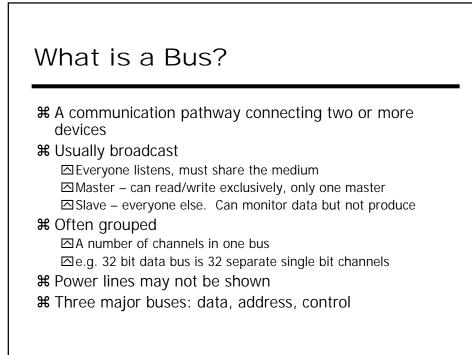

#### Buses

#There are a number of possible interconnection systems. The most common structure is the bus

- Single and multiple BUS structures are most common

- He.g. Control/Address/Data bus (PC)

- **#**e.g. Unibus (DEC-PDP) replaced the Omnibus

#### Data Bus

**℃**Carries data

□ Remember that there is no difference between "data" and "instruction" at this level

**#**Width is a key determinant of performance

△8, 16, 32, 64 bit

☑What if the data bus is 8 bits wide but instructions are 16 bits long?

☑What if the data bus is 64 bits wide but instructions are 16 bits long?

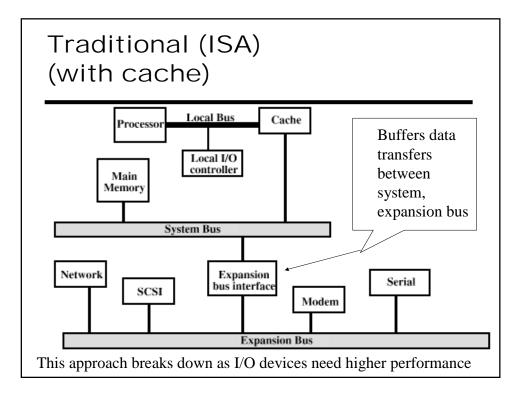

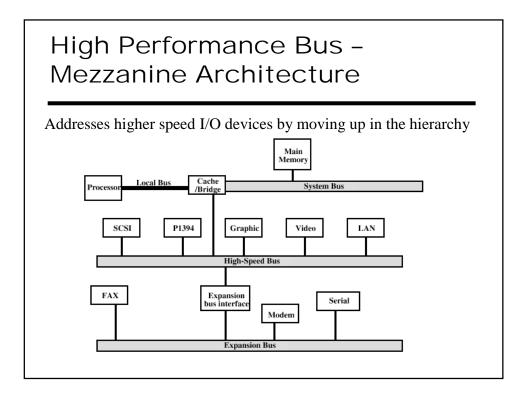

## Single Bus Problems

**#** Lots of devices on one bus leads to:

☐ Propagation delays

☑Long data paths mean that co-ordination of bus use can adversely affect performance – bus skew, data arrives at slightly different times

⊠ If aggregate data transfer approaches bus capacity. Could increase bus width, but expensive

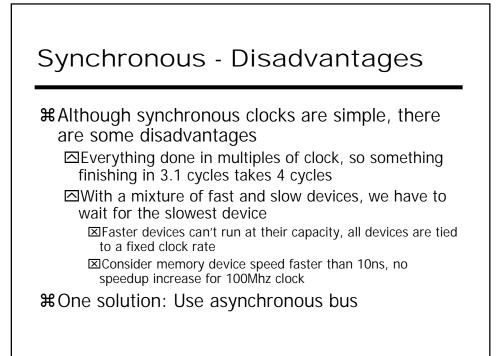

#### ⊡ Device speed

Bus can't transmit data faster than the slowest device

Slowest device may determine bus speed!

Consider a high-speed network module and a slow serial port on the same bus; must run at slow serial port speed so it can process data directed for it

#### ⊡ Power problems

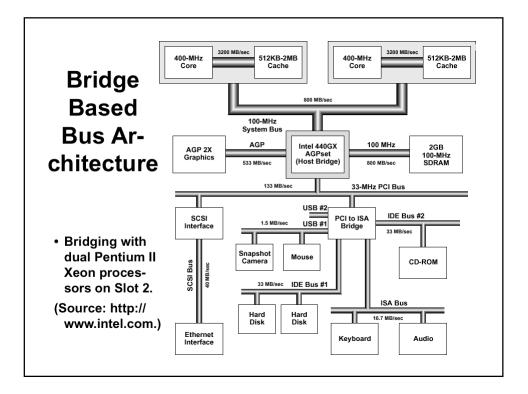

**#** Most systems use multiple buses to overcome these problems

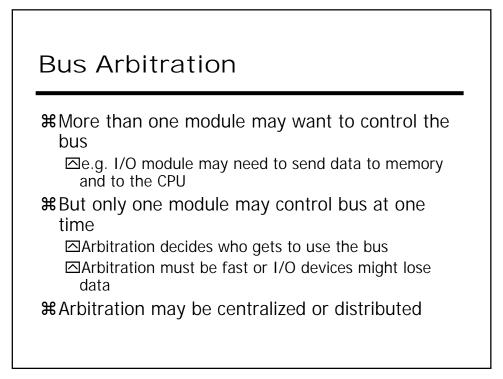

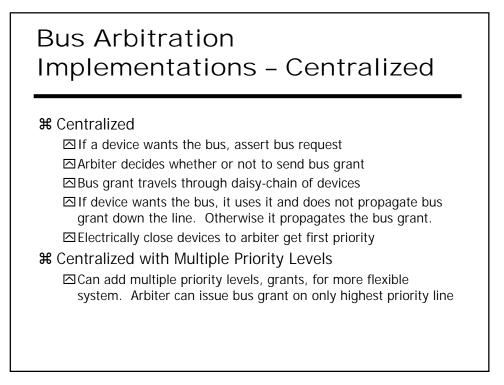

#### Centralized Arbitration

Single hardware device is responsible for allocating bus access

△Bus Controller

△Arbiter

Control CPU or separate

#### **Distributed Arbitration**

- **₭** No single arbiter

- **#** Each module may claim the bus

- **#** Proper control logic on all modules so they behave to share the bus

- # Purpose of both distributed and centralized is to designate the master

- **#** The recipient of a data transfer is the slave

- **#** Many types of arbitration algorithms: round-robin, priority, etc.

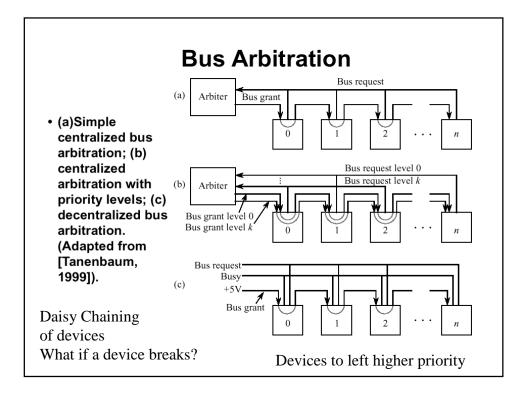

#### Bus Arbitration Implementation - Decentralized

#### **₩**Decentralized

- ☐ If don't want the bus, propagate bus grant down the line

- ☑To acquire bus, see if bus is idle and bus grant is on

☑If bus grant is off, may not become master, propagate negative bus grant

- ⊠If bus grant is on, propagate negative bus grant

- When dust settles, only one device has bus grant

- ☐ Asserts busy on and begins transfer

- □ Leftmost device that wants the bus gets it

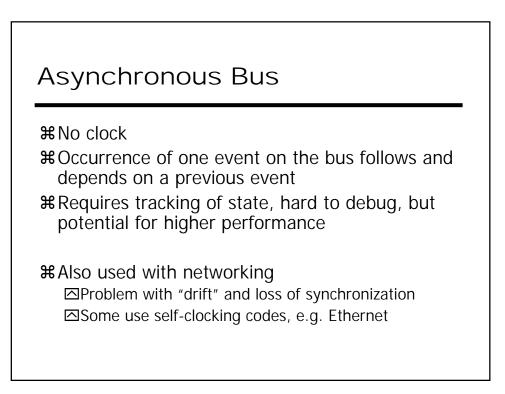

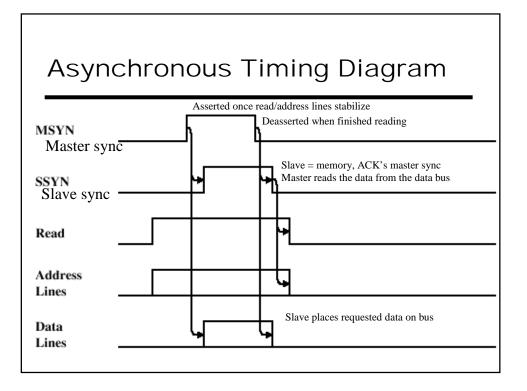

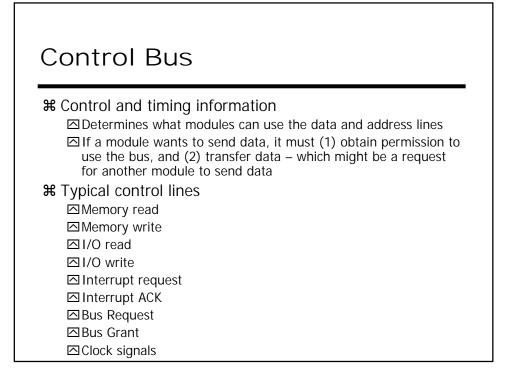

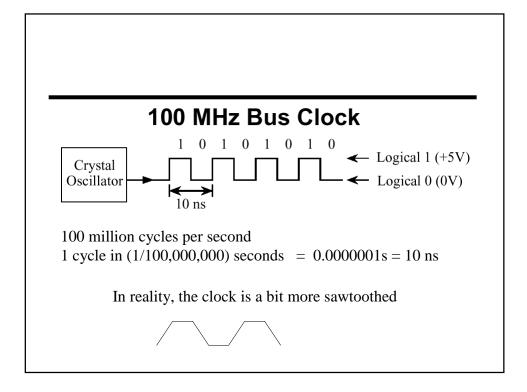

#### Timing

Co-ordination of events on bus

Synchronous

△Events determined by clock signals

△Control Bus includes clock line

△A single 1-0 is a bus cycle

△All devices can read clock line

△Usually sync on leading edge

△Usually a single cycle for an event

| Synchronous Timing Diagram<br>Read Operation Timing |                                                       |

|-----------------------------------------------------|-------------------------------------------------------|

| Clock                                               |                                                       |

| Start                                               | Indicates read/address lines valid, noticed by memory |

| Read                                                | Indicates we want to read, not write                  |

| Address<br>Lines                                    | Address from memory we want                           |

| Data<br>Lines                                       | delay Data from memory                                |

| Acknowledge                                         | Indicates data lines valid                            |